ARMv7-A uses the generic term exception to refer, in general terms, to interrupts and some other exception types like CPU errors. An interrupt is called an IRQ exception in ARMv7-A, so that’s the term the manual names a lot. When an ARMv7-A CPU takes an exception, it transfers control to an instruction located at the appropriate location in the vector table, depending on the exception type. The very first code we wrote for startup began with the vector table.

The IRQ, or normal interrupt request, is used for general purpose interrupt handling. It has a lower priority than an FIQ and is masked out when an FIQ sequence is entered. The IRQ is enabled to the core by clearing the I bit in the CPSR register and can be disabled by setting this bit. When an IRQ is detected by the core, it vectors to address 0x18 of the vector table and executes the instruction loaded in that address. Normally, the instruction found at 0x18 of the vector table is of the form:

LDR PC, IRQ_Handlerhttps://www.nxp.com/docs/en/application-note/AN2411.pdf

https://krinkinmu.github.io/2021/01/10/aarch64-interrupt-handling.html

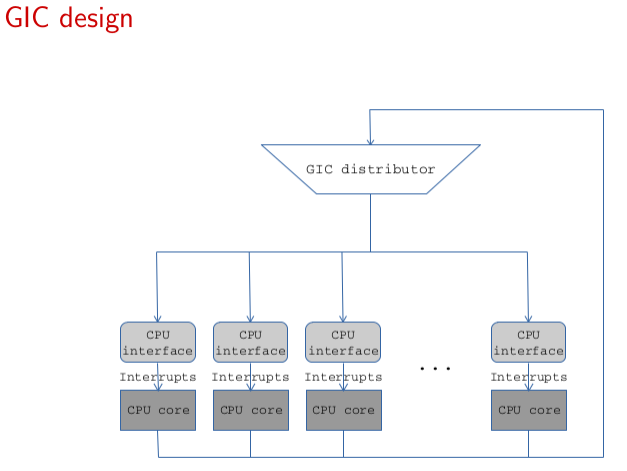

GENERIC INTERRUPT CONTROLLER