Let the ARM core be extended by additional hardware. I think it’s very close to Apple M1 strategy to implement hardware acceleration efficiently.

Coprocessors can be attached to the ARM processor. A coprocessor extends the processing features of a core by extending the instruction set or by providing configuration registers. More than one coprocessor can be added to the ARM core via the coprocessor interface. The coprocessor can be accessed through a group of dedicated ARM instructions (Instructions Reference) that provide a load-store type interface.

These new instructions are processed in the decode stage of the ARM pipeline. If the decode stage sees a coprocessor instruction, then it offers it to the relevant coprocessor. But if the coprocessor is not present or doesn’t recognize the instruction, then the ARM takes an undefined instruction exception, which allows you to emulate the behavior of the coprocessor in software.

The ARM instruction set supports the connection of 16 coprocessors, numbered 0-15, to an ARM processor. In the processor, the following coprocessor numbers are reserved:

- **CP10 - **VFP control

- **CP11 - **VFP control

- **CP14 - **Debug and ETM control

- **CP15 - **System control.

You can use CP0-9, CP12, and CP13 for your own external coprocessors.

Move to ARM Register from Coprocessor. Depending on the coprocessor, you might be able to specify various additional operations.

Syntax:

MRC{cond} coproc, #opcode1, Rt, CRn, CRm{, #opcode2}MRC2{cond} coproc, #opcode1, Rt, CRn, CRm{, #opcode2}Where:

**cond**is an optional condition code. In ARM code,condis not permitted forMRC2.**coproc**** **is the name of the coprocessor the instruction is for. The standard name is pn, wherenis an integer in the range 0 to 15.**opcode1**is a 3-bit coprocessor-specific opcode.**opcode2**is an optional 3-bit coprocessor-specific opcode.**Rt**is the ARM destination register.Rtmust not be PC.Rtcan beAPSR_nzcv. This means that the coprocessor executes an instruction that changes the value of the condition flags in the APSR.**CRn****, ****CRm**are coprocessor registers.

Example:

Random chat with a friend about the “coprocessor” feature on ARM:

sargx — Hoje às 17:21

@Kaguya Nopano vc sabe se no x86_64 tem como expandir a funcionalidade do core principal? ou algo do tipo?

Kaguya Nopano — Hoje às 17:25

em que sentido "expandir"?

sargx — Hoje às 17:26

pq no ARM existe uma parada que chama "coprocessadores", que basicamente vc consegue expandir o processador adicionando hardwares paralelos... Esse "hardware" pode ser um acelerador de operações de criptografia por exemplo. A questão é que isso não é feito via MMIO, o ARM deixa vc anexar esse "coprocessador"/hardware direto na BUS

oq eu acredito que reduz bem a latência entre a comunicação do core com o periférico

sargx — Hoje às 17:34

e acho q é oq o Apple M1 implementa isso para usar os aceleradores que eles dizem ter implementado em hardware (e que funcionam muito bem)

Kaguya Nopano — Hoje às 17:47

não me lembro de nada de cabeça que seja parecido com isso em x86

sargx — Hoje às 17:49

então... pesquisando eu tbm n encontrei nada

mas estou certo de pensar que integrar direto a bus é mais rápido que MMIO?

pq usando MMIO, o processador ainda tem que garantir nível de privilégio, contexto e etc, certo?

Kaguya Nopano — Hoje às 17:52

s

é o que eu pensaria tb

eu teria que estudar mais a fundo isso aí para chegar numa conclusão melhor

então por enquanto minha resposta é só essa

sargx — Hoje às 17:56

blz

sargx — Hoje às 17:56

tranquilo, estou questionando só pra saber se n estou com uma visão muito torta das coisas

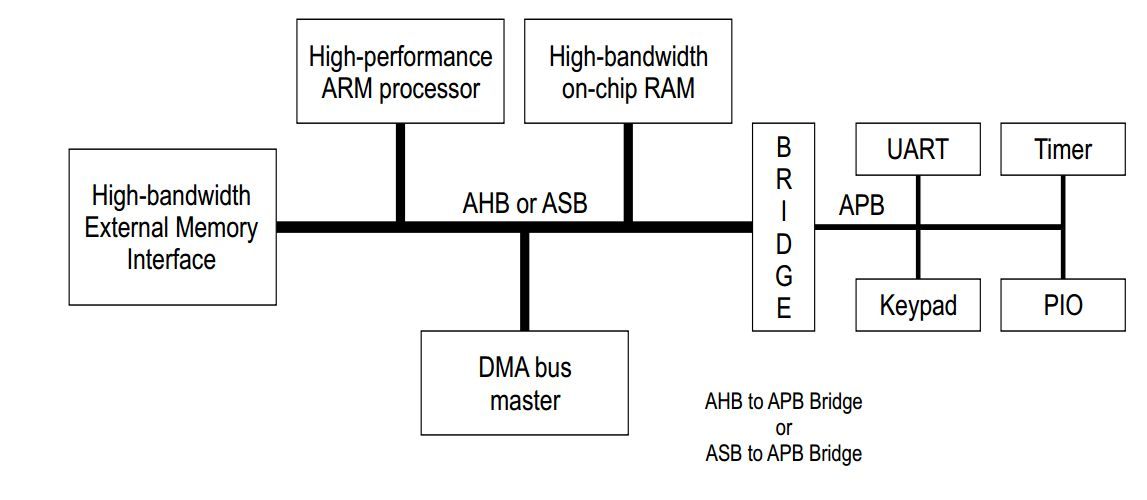

AMBA is an open-standard that outlines how to connect and manage the different components or blocks within an SoC. The AMBA specification was developed by ARM and has become the de facto standard for interfacing components in an SoC. While AMBA is currently on its 5th revision and has evolved significantly over time, legacy implementations are widely used and remain relevant. Keeping that in mind, this article will use Revision 2.0 as a starting point and build off of these ideas in a future article.

AMBA 5 AHB5 (Advanced High Performance Bus)

https://www.arm.com/resources/education/books/modern-soc

https://www.arm.com/resources/ebook/fundamentals-of-soc

https://armkeil.blob.core.windows.net/developer/Files/pdf/ebook/arm-fundamental-soc.pdf