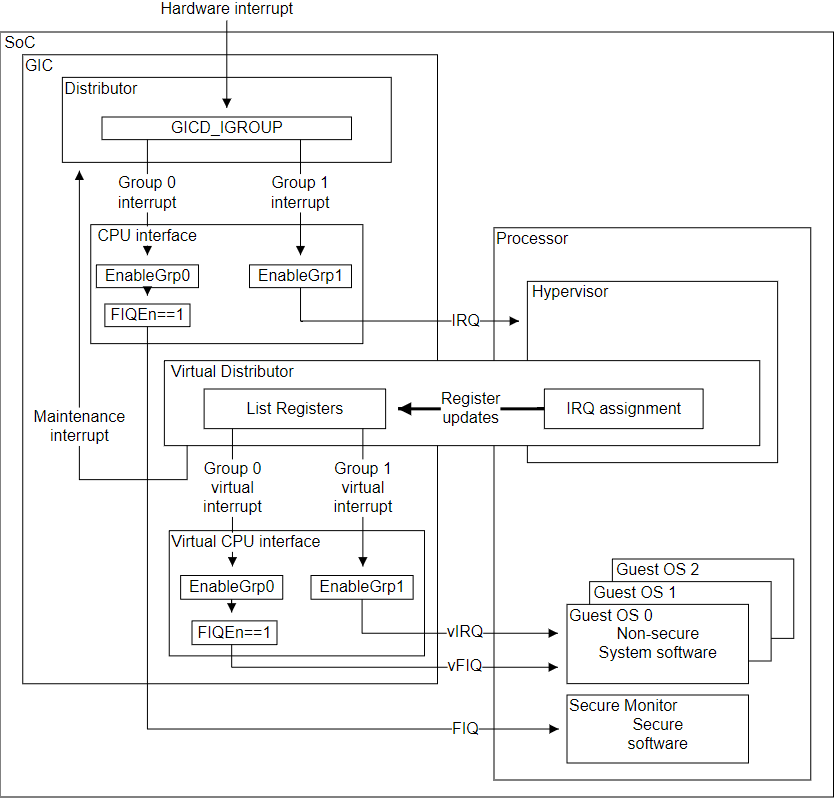

The GICv3 architecture defines a virtual GIC (vGIC) interface for each CPU that provides virtual interrupt management capabilities to a hypervisor. When virtual interrupts are enabled, all physical interrupts are routed to EL2.

Before the target VM is scheduled on a physical CPU, the hypervisor signals for a virtual interrupt to be delivered once execution has returned to EL1. If a VM attempts to configure the GIC distributor through the MMIO interface, the second stage of translation will trap execution into EL2 where the hypervisor can emulate the operation.

VM accesses to the GIC system registers are routed to a set of virtual system registers, which control virtual interrupt delivery. During a virtual CPU context switch, the hypervisor must save the writable virtual system register state, the state of any pending virtual interrupts, and the VM specific virtual interrupt configuration.